Термин архитектура вычислительной машины впервые был употреблен для

Гарвардская архитектура

Гарвардская архитектура — архитектура ЭВМ, отличительными признаками которой являются:

1. Хранилище инструкций и хранилище данных представляют собой разные физические устройства.

2. Канал инструкций и канал данных также физически разделены.

Архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете.

Содержание

История

Классическая гарвардская архитектура

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий:

Идея, реализованная Эйкеном, заключалась в физическом разделении линий передачи команд и данных. В первом компьютере Эйкена «Марк I» для хранения инструкций использовалась перфорированная лента, а для работы с данными — электромеханические регистры. Это позволяло одновременно пересылать и обрабатывать команды и данные, благодаря чему значительно повышалось общее быстродействие компьютера.

В Гарвардской архитектуре характеристики устройств памяти для инструкций и памяти для данных не требуется иметь общими. В частности, ширина слова, тайминги, технология реализации и структура адресов памяти могут различаться. В некоторых системах инструкции могут храниться в памяти только для чтения, в то время как для сохранения данных обычно требуется память с возможностью чтения и записи. В некоторых системах требуется значительно больше памяти для инструкций, чем памяти для данных, поскольку данные обычно могут подгружатся с внешней или более медленной памяти. Такая потребность увеличивает битность (ширину) шины адреса памяти инструкций по сравнению с шиной адреса памяти данных.

Отличие от архитектуры фон Неймана

В чистой архитектуре фон Неймана процессор одномоментно может либо читать инструкцию, либо читать/записывать единицу данных из/в памяти. То и другое не может происходить одновременно, поскольку инструкции и данные используют одну и ту же системную шину.

А в компьютере с использованием гарвардской архитектуры процессор может читать инструкции и выполнять доступ к памяти данных в то же самое время, даже без кэш-памяти. Таким образом, компьютер с гарвардской архитектурой может быть быстрее (при определенной сложности схемы), поскольку доставка инструкций и доступ к данным не претендуют на один и тот же канал памяти.

Также машина гарвардской архитектуры имеет различные адресные пространства для команд и данных. Так, нулевой адрес инструкций — это не то же самое, что и нулевой адрес данных. Нулевой адрес инструкций может определяться двадцатичетырехбитным значением, в то время как нулевой адрес данных может выглядеть как восьмибитный байт, который не являются частью этого двадцатичетырехбитного значения.

Модифицированная гарвардская архитектура

Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи команд и данных на кристалле процессора последний должен иметь почти вдвое больше выводов, так как шина адреса и шина данных составляют основную часть выводов микропроцессора. Способом решения этой проблемы стала идея использовать общие шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной Гарвардской архитектурой.

Такой подход применяется в современных сигнальных процессорах. Ещё дальше по пути уменьшения стоимости пошли при создании однокристалльных ЭВМ — микроконтроллеров. В них одна шина команд и данных применяется и внутри кристалла.

Разделение шин в модифицированной Гарвардской структуре осуществляется при помощи раздельных управляющих сигналов: чтения, записи или выбора области памяти.

Расширенная гарвардская архитектура

Часто требуется выбрать три составляющие : два операнда и инструкцию (в алгоритмах цифровой обработки сигналов это наиболее распространенная задача в БПФ и КИХ, БИХ фильтрах). Для этого существует кэш-память. В ней может храниться инструкция — следовательно, обе шины остаются свободными и появляется возможность передать два операнда одновременно. Использование кэш-памяти вместе с разделёнными шинами получило название «Super Harvard Architecture» («SHARC») — расширенная Гарвардская архитектура.

Примером могут служить процессоры «Analog Devices»: ADSP-21xx — модифицированная Гарвардская Архитектура, ADSP-21xxx(SHARC) — расширенная Гарвардская Архитектура.

Гибридные модификации с архитектурой фон Неймана

Существуют гибридные архитектуры, сочетающие достоинства как Гарвардской так и фон Неймановской архитектур. Современные CISC-процессоры обладают раздельной кэш-памятью 1-го уровня для инструкций и данных, что позволяет им за один рабочий такт получать одновременно и команду, и данные для её выполнения. То есть процессорное ядро, формально, является гарвардским, но программно оно фон Неймановское, что упрощает написание программ. Обычно в данных процессорах одна шина используется и для передачи команд, и для передачи данных, что упрощает конструкцию системы. Современные варианты таких процессоров могут иногда содержать встроенные контроллеры сразу нескольких разнотипных шин для работы с различными типами памяти — например, DDR RAM и Flash. Тем не менее, и в этом случае шины, как правило, используются и для передачи команд, и для передачи данных без разделения, что делает данные процессоры ещё более близкими к фон Неймановской архитектуре при сохранении плюсов Гарвардской архитектуры.

Использование

Первым компьютером, в котором была использована идея гарвардской архитектуры, был Марк I. Гарвардская архитектура используется в ПЛК и микроконтроллерах, таких, как Microchip PIC, Atmel AVR, Intel 4004, Intel 8051.

Архитектура вычислительных машин

Различают Принстонскую и Гарвардскую архитектуру вычислительных машин. Эти архитектурные варианты были предложены в конце 40-х годов специалистами, соответственно, Принстонского и Гарвардского университетов США для разрабатываемых ими моделей компьютеров.

Принстонская архитектура

Любую вычислительную машину образуют три основные компонента:

Информационная связь между устройствами компьютера осуществляется через системную шину (системную магистраль).

Системная шина, в свою очередь, представляет собой совокупность

Тактовая частота характеризует число элементарных операций по передаче данных в 1 секунду. Разрядность шины измеряется в битах, тактовая частота – в мегагерцах.

Устройство управления (УУ) формирует адрес команды, которая должна быть выполнена в данном цикле, и выдает управляющий сигнал на чтение содержимого соответствующей ячейки запоминающего устройства (ЗУ). Считанная команда передается в УУ. По информации, содержащейся в адресных полях команды, УУ формирует адреса операндов и управляющие сигналы для их чтения из ЗУ и передачи в арифметико-логическое устройство (АЛУ). После считывания операндов устройство управления по коду операции, содержащемуся в команде, выдает в АЛУ сигналы на выполнение операции. Полученный результат записывается в ЗУ по адресу приемника результата под управлением сигналов записи. Признаки результата (знак, наличие переполнения, признак нуля и так далее) поступают в устройство управления, где записываются в специальный регистр признаков. Эта информация может использоваться при выполнении следующих команд программы, например команд условного перехода.

Устройство ввода позволяет ввести программу решения задачи и исходные данные в ЭВМ и поместить их в оперативную память. В зависимости от типа устройства ввода исходные данные для решения задачи вводятся непосредственно с клавиатуры, либо они должны быть предварительно помещены на какой-либо носитель (дисковый накопитель).

Устройство вывода служит для вывода из ЭВМ результатов обработки исходной информации. Чаще всего это символьная информация, которая выводится с помощью печатающих устройств или на экран дисплея.

Обработка данных и команд осуществляется посредством арифметико-логического устройства (АЛУ), предназначенного для непосредственного выполнения машинных команд под действием устройства управления. АЛУ и УУ совместно образуют центральное процессорное устройство (ЦПУ). Результаты обработки передаются в память.

Основные принципы построения вычислительных машин с архитектурой фон Неймана

Архитектура фон Неймана имеет ряд важных достоинств.

Поэтому Принстонская архитектура в течение долгого времени доминировала в вычислительной технике.

Однако ей присущи и существенные недостатки. Основным из них является необходимость последовательной выборки команд и обрабатываемых данных по общей системной шине. При этом общая шина становится «узким местом» (bottleneck – «бутылочное горло»), которое ограничивает производительность цифровой системы.

Гарвардская архитектура

Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти. Она характеризуется физическим разделением памяти команд (программ) и памяти данных. В ее оригинальном варианте использовался также отдельный стек для хранения содержимого программного счетчика, который обеспечивал возможности выполнения вложенных подпрограмм. Каждая память соединяется с процессором отдельной шиной, что позволяет одновременно с чтением-записью данных при выполнении текущей команды производить выборку и декодирование следующей команды. Благодаря такому разделению потоков команд и данных и совмещению операций их выборки реализуется более высокая производительность, чем при использовании Принстонской архитектуры.

Недостатки Гарвардской архитектуры связаны с необходимостью проведения большего числа шин, а также с фиксированным объемом памяти, выделенной для команд и данных, назначение которой не может оперативно перераспределяться в соответствии с требованиями решаемой задачи. Поэтому приходится использовать память большего объема, коэффициент использования которой при решении разнообразных задач оказывается более низким, чем в системах с Принстонской архитектурой. Однако развитие микроэлектронной технологии позволило в значительной степени преодолеть указанные недостатки, поэтому Гарвардская архитектура широко применяется во внутренней структуре современных высокопроизводительных микропроцессоров, где используется отдельная кэш-память для хранения команд и данных. В то же время во внешней структуре большинства микропроцессорных систем реализуются принципы Принстонской архитектуры.

Термин архитектура вычислительной машины впервые был употреблен для

Основы учения об архитектуре вычислительных машин были заложены выдающимся американским математиком Джоном фон Нейманом. Он присоединился к разработке и созданию первой в мире ламповой ЭВМ ENIAC в 1944 г., в то время когда конструкция ENIAC уже была выбрана. В период трудоемкой работы с коллегами ( Г. Голдстайном и А. Берксом ), фон Нейман предложил идею концептуально новой ЭВМ. И уже в 1946 г. ученые предоставили свою работу по построению вычислительной машины в ставшей классической статье «Предварительное рассмотрение логической конструкции электронно-вычислительного устройства». С того момента прошло уже больше полувека, но представленные в ней теория и положения до сих пор имеют фундаментальную ценность. Раньше все ЭВМ хранили и обрабатывали числа в десятичном коде. Фон Нейман с коллегами представил факты, которые подтверждали преимущества двоичной системы для технической части, с использованием этой системы можно было удобно и просто выполнять арифметические и логические операций. С развитием ЭВМ человечество стало обрабатывать не только нечисловые виды информации, но и текстовую, графическую, звуковую и другие виды информации. До сих пор двоичная кодировка данных продолжает составлять информационный “фундамент” любого современного компьютера.

Первыми электронными вычислительными машинами (ЭВМ) могли пользоваться только сотрудники крупных лабораторий и научно-исследовательских центров. Это было связано не только с их высокой стоимостью, но и с относительно большими размерами самих ЭВМ. И то, что в современном мире компьютеры можно встретить в офисах, школах, детских садах, квартирах, стало возможным благодаря разработке микропроцессора, который позволил значительно уменьшить размеры компьютера, сделав его действительно персональным устройством.

В 1969 году фирма Intel получила от японской компании Busicom заказ на разработку набора из 12 микросхем для семейства программируемых калькуляторов. В то время все микросхемы, выполняющие вычисления, разрабатывались специально под продукт заказчика. Однако сотрудники Intel Тед Хофф, Федерико Феджин и Стен Мэйзор предложили спроектировать единую универсальную микросхему — центральный процессор ЭВМ общего назначения, который взял бы на себя все функции отдельных микросхем. Главная особенность этого процессора заключалась в том, что в нем несколько интегральных микросхем размещались на одном кристалле кремния. Хофф разработал архитектуру микропроцессора, Мэйзор — систему команд, а Феджин спроектировал саму микросхему.

15 ноября 1971 года фирма Intel представила миру первый четырехразрядный микропроцессор, названный i 4004 (рисунок 2).

Первым микрокомпьютером, который привлек внимание потребителей, стал Altair 8800 (рисунок 3) фирмы MITS (1975 г.).

Рисунок 4 – Персональный компьютер Аррlе-2

Открытая архитектура персонального компьютера — это архитектура, предусматривающая модульное построение компьютера с возможностью добавления и замены отдельных устройств благодаря наличию опубликованной документации на эти устройства.

Первый персональный компьютер фирмы IBM был выпущен в 1981 году и назван IBM PC model 5150. Он использовал процессор i 8088 фирмы Intel с тактовой частотой 4,77 МГц. Объем оперативной памяти составлял 64 Кбайт. Устройства долговременной памяти отсутствовали. Для этого процессора фирмой Microsoft была разработана новая операционная система MS — DOS .

В 1984 году фирма Apple выпустила первый персональный компьютер, в которым был графический интерфейс пользователя вместо стандартного на тот момент интерфейса командной строки. Для работы с этим интерфейсом впервые стало массово применяться новое устройство — мышь. Компьютер был назван Macintosh (рисунок 5).

Рисунок 5 – Первый персональный компьютер с графическим интерфейсом, Macintosh

Герман Хайн Голдстайн — математик, один из создателей первой из современных ЭВМ — ENIAC.

Архитектура вычислительной машины

Архитектура вычислительной машины (Архитектура ЭВМ, англ. Computer architecture) — концептуальная структура вычислительной машины, определяющая проведение обработки информации и включающая методы преобразования информации в данные и принципы взаимодействия технических средств и программного обеспечения.

В настоящее время наибольшее распространение в ЭВМ получили 2 типа архитектуры: принстонская (фон Неймана) и гарвардская. Обе они выделяют 2 основных узла ЭВМ: центральный процессор и память компьютера. Различие заключается в структуре памяти: в принстонской архитектуре программы и данные хранятся в одном массиве памяти и передаются в процессор по одному каналу, тогда как гарвардская архитектура предусматривает отдельные хранилища и потоки передачи для команд и данных.

В более подробное описание, определяющее конкретную архитектуру, также входят: структурная схема ЭВМ, средства и способы доступа к элементам этой структурной схемы, организация и разрядность интерфейсов ЭВМ, набор и доступность регистров, организация памяти и способы её адресации, набор и формат машинных команд процессора, способы представления и форматы данных, правила обработки прерываний.

По перечисленным признакам и их сочетаниям среди архитектур выделяют:

· По разрядности интерфейсов и машинных слов: 8-, 16-, 32-, 64-разрядные (ряд ЭВМ имеет и иные разрядности);

· По особенностям набора регистров, формата команд и данных: CISC, RISC, VLIW;

· По количеству центральных процессоров: однопроцессорные, многопроцессорные, суперскалярные;

· многопроцессорные по принципу взаимодействия с памятью: симметричные многопроцессорные (SMP), масcивно-параллельные (MPP), распределенные.

RISC (англ. Restricted (reduced) instruction set computer — компьютер с сокращённым набором команд) — архитектура процессора, в которой быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — короче. Первые RISC-процессоры даже не имели инструкций умножения и деления. Это также облегчает повышение тактовой частоты и делает более эффективной суперскалярность (распараллеливание инструкций между несколькими исполнительными блоками).

Наборы инструкций в более ранних архитектурах для облегчения ручного написания программ на языках ассемблеров или прямо в машинных кодах, а также для упрощения реализации компиляторов, выполняли как можно больше работы. Нередко в наборы включались инструкции для прямой поддержки конструкций языков высокого уровня. Другая особенность этих наборов — большинство инструкций, как правило, допускали все возможные методы адресации (т. н. «ортогональность системы команд (англ.)») — к примеру, и операнды, и результат в арифметических операциях доступны не только в регистрах, но и через непосредственную адресацию, и прямо в памяти. Позднее такие архитектуры были названы CISC (англ. Complex instruction set computer).

Однако многие компиляторы не задействовали все возможности таких наборов инструкций, а на сложные методы адресации уходит много времени из-за дополнительных обращений к медленной памяти. Было показано, что такие функции лучше исполнять последовательностью более простых инструкций, если при этом процессор упрощается и в нём остаётся место для большего числа регистров, за счёт которых можно сократить количество обращений к памяти. В первых архитектурах, причисляемых к RISC, большинство инструкций для упрощения декодирования имеют одинаковую длину и похожую структуру, арифметические операции работают только с регистрами, а работа с памятью идёт через отдельные инструкции загрузки (load) и сохранения (store). Эти свойства и позволили лучше сбалансировать этапы конвейеризации, сделав конвейеры в RISC значительно более эффективными и позволив поднять тактовую частоту.

CISC (англ. сomplex instruction set computing, или англ. complex instruction set computer — компьютер с полным набором команд) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

· нефиксированное значение длины команды;

· арифметические действия кодируются в одной команде;

· небольшое число регистров, каждый из которых выполняет строго определённую функцию.

Типичными представителями являются процессоры на основе x86-команд (исключая современные Intel Pentium 4, Pentium D, Core, AMD Athlon, Phenom, которые являются гибридными) и процессоры Motorola MC680x0.

Наиболее распространённая архитектура современных настольных, серверных и мобильных процессоров построена по архитектуре Intel x86 (или х86-64 в случае 64-разрядных процессоров). Формально все х86-процессоры являлись CISC-процессорами, однако новые процессоры, начиная с Intel 486DX, являются CISC-процессорами с RISC-ядром. Они непосредственно перед исполнением преобразуют CISC-инструкции процессоров x86 в более простой набор внутренних инструкций RISC.

В микропроцессор встраивается аппаратный транслятор, превращающий команды x86 в команды внутреннего RISC-процессора. При этом одна команда x86 может порождать несколько RISC-команд (в случае процессоров типа P6 — до четырёх RISC-команд в большинстве случаев). Исполнение команд происходит на суперскалярном конвейере одновременно по несколько штук.

Это потребовалось для увеличения скорости обработки CISC-команд, так как известно, что любой CISC-процессор уступает RISC-процессорам по количеству выполняемых операций в секунду. В итоге такой подход и позволил поднять производительность CPU

VLIW (англ. very long instruction word — «очень длинная машинная команда») — архитектура процессоров с несколькими вычислительными устройствами. Характеризуется тем, что одна инструкция процессора содержит несколько операций, которые должны выполняться параллельно. Фактически это «видимое программисту» микропрограммное управление, когда машинный код представляет собой лишь немного свернутый микрокод) для непосредственного управления аппаратурой.

В суперскалярных процессорах также есть несколько вычислительных модулей, но задача распределения между ними работы решается аппаратно. Это сильно усложняет дизайн процессора, и может быть чревато ошибками. В процессорах VLIW задача распределения решается во время компиляции и в инструкциях явно указано, какое вычислительное устройство должно выполнять какую команду.

VLIW можно считать логическим продолжением идеологии RISC, расширяющей её на архитектуры с несколькими вычислительными модулями. Так же, как в RISC, в инструкции явно указывается, что именно должен делать каждый модуль процессора. Из-за этого длина инструкции может достигать 128 или даже 256 бит.

Первое поколение компьютеров: от Древнего Рима до Второй Мировой

Лень — двигатель прогресса. Стремление человечества хотя бы частично автоматизировать свою деятельность всегда выливалось в различные изобретения. Математические вычисления и подсчеты также не избежали научного прогресса. Ещё в Древнем Риме местные «таксисты» использовали аналог современного таксометра — механическое устройство, которое определяло стоимость поездки в зависимости от длины маршрута. Время шло, и к середине прошлого века эволюция вычислительных систем привела к появлению нового типа устройств — компьютеров. Тогда, конечно, их так никто не называл. Для этого использовался другой термин — ЭВМ (электронно-вычислительная машина). Но время и прогресс стерли границы между этими определениями. Так как же прогресс дошел до первых ЭВМ и как они работали?

История развития

Арифмометр

Данная машина представляла собой 13-разрядную суммирующую машину.

В следующем году вокруг этой машины начали появляться различные возражения, а именно по поводу её механизма. Существовало мнение о том, что машина да Винчи представляет собой механизм пропорционирования, а не счетную машину. Также возникал вопрос и о её работе: по идее, 1 оборот первой оси вызывает 10 оборотов второй, 100 оборотов третьей и 10 в степени n оборотов n-ной оси. Работа такого механизма не могла осуществляться из-за огромной силы трения. По итогу голоса сторонников и противников счетной машины Леонардо да Винчи разделились, но, тем не менее, IBM решила убрать эту модель из коллекции

Но, оставим наработки Леонардо Да Винчи. Расцвет арифмометров пришелся на 17 век. Первой построенной моделью стал арифмометр Вильгельма Шиккарда в 1623 году. Его машина была 6-разрядной и состояла из 3 блоков — множительного устройства, блока сложения-вычитания и блока записи промежуточных результатов.

Копия арифмометра Шиккарда

Также 17 век отметился ещё несколькими арифмометрами: «паскалина» за авторством Блеза Паскаля, арифмометр Лейбница и машина Сэмюэля Морленда. В промышленных масштабах арифмометры начали производиться в начале 19 века, а распространены были практически до конца 20-го.

Аналитическая и разностная машины Бэббиджа

Чарльз Бэббидж — английский математик, родившийся в конце 18 века. На его счету числится большое количество научных работ и изобретений. Но в рамках данной статьи нас интересуют два его проекта: аналитическая машина и разностная машина.

Идея о создании разностной машины не принадлежит Чарльзу Бэббиджу. Она впервые была описана немецким инженером Иоганном Мюллером в книге с очень сложным названием. До конца не ясно, повлияли ли на Бэббиджа идеи Мюллера при создании разностной машины, поскольку Чарльз ознакомился с его работой в переводе, дата создания которого неизвестна.

Книга Иоганна Мюллера

Считается, что основные идеи для создания разностной машины Бэббидж взял из работ Гаспара де Прони и его идей о декомпозиции математических работ. Его идея заключалась в следующем: есть 3 уровня, на каждом из которых математики занимаются решением определенных проблем. На верхнем уровне находятся самые крутые математики и их задача — вывод математических выражений, пригодных для расчетов. У математиков на втором уровне стояла задача вычислять значения функций, которые вывели на верхнем уровне, для аргументов, с определенным периодом. Эти значения становились опорными для третьего уровня, задачей которого являлись рутинные расчеты. От них требовалось делать только грамотные вычисления. Их так и называли — «вычислители». Эта идея навела Бэббиджа на мысль о создании машины, которая могла бы заменить «вычислителей». Машина Бэббиджа основывалась на методе аппроксимации функций многочленами и вычисления конечных разностей. Собственно, поэтому машина и называется разностной.

В 1822 году Бэббидж построил модель разностной машины и заручился государственной поддержкой в размере 1500 фунтов стерлингов. Он планировал, что закончит машину в течение 3 лет, но по итогу работа была не завершена и через 9 лет. За это время он получил ещё 15500 фунтов стерлингов в виде субсидий от государства. Но всё же часть машины функционировала и производила довольно точные (>18 знаков после запятой) расчеты.

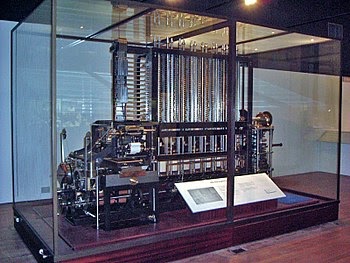

Созданная на основе работ Бэббиджа разностная машина

Во время работы над разностной машиной у Чарльза Бэббиджа возникла идея о создании аналитической машины — универсальной вычислительной машины. Её называют прообразом современного цифрового компьютера, и не зря. Она состояла из арифметического устройства (»мельницы»), памяти (»склада») и устройства ввода-вывода, реализованного с помощью перфокарт различного типа. К сожалению, данная идея осталась лишь на бумаге.

Схема аналитической машины Бэббиджа

Табулятор

История электромеханических машин начинается в 1888 году, когда американский инженер Герман Холлерит, основатель компании CTR (будущая IBM), изобрел электромеханическую счетную машину — табулятор, который мог считывать и сортировать данные, закодированные на перфокартах. В аппарате использовались электромагнитные реле, известные еще с 1831 года и до Холлерита не применявшиеся в счетной технике. Управление механическими счетчиками и сортировкой осуществлялось электрическими импульсами, возникающими при замыкании электрической цепи при наличии отверстия в перфокарте. Импульсы использовались и для ввода чисел, и для управления работой машины. Поэтому табулятор Холлерита можно считать первой счетной электромеханической машиной с программным управлением. Машину полностью построили в 1890 году и использовали при переписи населения США в том же году. Впоследствии табуляторы использовались вплоть до 1960-х — 1970-х годов в бухгалтерии, учете, обработке данных переписей и подобных работах. И даже если в учреждении имелась полноценная ЭВМ, табуляторы все равно использовали, чтобы не нагружать ЭВМ мелкими задачами.

Электромеханические машины времен ВМВ

В 1937 году Клод Шеннон в своей работе A Symbolic Analysis of Relay and Switching Circuits показал, что электронные связи и переключатели могут представлять выражения булевой алгебры. Машины тех лет можно условно на два типа: электромеханические (основанные на электромагнитных переключателях) и электронные (полностью на электровакуумных лампах). К первым относились американский Harvard Mark I и компьютеры немецкого инженера Конрада Цузе.

Mark I

Работа над Mark I началась в 1939 году в Endicott laboratories по субподрядному договору с IBM. В качестве основы использовались наработки Чарльза Бэббиджа. Компьютер последовательно считывал инструкции с перфоленты, условного перехода не было, циклы организовывались в виде склеенных в кольцо кусков перфоленты. Принцип разделения данных и инструкций в Mark I получил известность как Гарвардская архитектура. Машину закончили в 1944 году и передали в ВМФ США. Характеристики:

В 1936 немецкий инженер Конрад Цузе начал работу над своим первым вычислителем Z1. Первые две модели из серии Z были демонстративными. Следующий же компьютер, Z3, который закончили в 1941, имел практическое применение: с его помощью делали аэродинамические расчеты (стреловидные крылья самолетов, управляемые ракеты). Машина была выполнена на основе телефонных реле. Инструкции считывались с перфорированной пленки. Так же, как в Mark I, отсутствовали инструкции условного перехода, а циклы реализовывались закольцованной перфолентой. Z3 имел некоторые преимущества перед своими будущими собратьями (ENIAC, Mark I): вычисления производились в двоичной системе, устройство позволяло оперировать числами с плавающей точкой. Так как Цузе изначально исходил из гражданских интересов, его компьютеры более близки к современным, чем тогдашние аналоги. В 1944 году практически был завершен Z4, в котором уже присутствовали инструкции условного перехода. Характеристики Z3:

Первые ламповые компьютеры

Однозначно определить первый в мире компьютер сложно. Многими учеными определение первого поколения основывается на вычислительной базе из электронных ламп. При этом первое поколение компьютеров разрабатывалось во время Второй мировой войны. Возможно, созданные в то время компьютеры засекречены и по сей день. В целом выделяют два возможных первенца — ENIAC и Colossus

ENIAC

Electronic Numerical Integrator and Computer (Электронный числовой интегратор и вычислитель) или ENIAC создавался по заказу от армии США для расчета баллистических таблиц. Изначально, подобные расчеты производились людьми и их скорость не могла соотноситься с масштабом военных действий. Построен компьютер был лишь к осени 1945 года.

Colossus

Colossus в отличие от ENIAC был очень узконаправленной машиной. Он создавался исключительно с одной целью — декодирование немецких сообщений, зашифрованных с помощью Lorenz SZ. Эта машина было схожа с немецкой Enigma, но состояла из большего числа роторов. Для декодирования этих сообщений было решено создать Colossus. Он включал в себя 1500 электронных ламп, потреблял 8,5 КВт и обладал тактовой частотой в 5.8 МГц. Такое значение частоты достигалось за счет того, что Colossus был создан для решения только одной задачи и применяться в других областях не мог. К концу войны на вооружении Британии стояло 10 таких машин. После войны все они были уничтожены, а данные о них засекречены. Только в 2000 году эта информация была рассекречена.

Реконструированная модель Colossus

Принцип работы

Вакуумные лампы

Радиолампа представляет собой стеклянную колбу с электродами, из которой откачан воздух. Простейшая разновидность ламп — диод, состоящий из катода и анода, а также спирали, разогревающей катод до температур, при которых начинается термоэлектронная эмиссия. Электроны покидают катод и под действием разности потенциалов притягиваются к аноду. В обратном направлении заряд не переносится, так как заряженных ионов в колбе нет (вакуум). При изменении полярности электроны, покинувшие разогретый электрод, будут притягиваться обратно. До второго электрода они долетать не будут, отталкиваясь от него из-за отрицательного потенциала. Если добавить еще один электрод, то получится триод. В электровакуумном триоде устанавливается сетка между катодом и анодом. При подаче на сетку отрицательного потенциала она начинает отталкивать электроны, не позволяя им достичь анода. При подаче модулированного сигнала ток будет повторять изменения потенциала на сетке, поэтому изначально триоды использовали для усиления сигналов.

Радиолампа и схема триггера на двух триодах

Если взять два триода и соединить анод каждого с сеткой другого, то мы получим триггер. Он может находиться в одном из двух состояний: если через один триод идет ток (триод открыт), то на сетке второго триода появляется потенциал, препятствующий току через второй триод (триод закрыт). Если кратковременно подать отрицательный потенциал на сетку открытого триода, то мы прекратим ток через него, что откроет второй триод, который уже закроет первый. Триоды поменяются местами. Таким образом можно хранить один бит информации. Через другие схемы триодов можно строить логические вентили, реализующие конъюнкцию, дизъюнкцию и отрицание, что позволяет создать электронно-вычислительное устройство.

Запоминающее устройство

На первых порах развития ЭВМ использовались разные подходы к созданию запоминающих устройств. Помимо памяти на триггерах из радиоламп и на электромагнитных реле (как в Z3) имелись следующие виды:

Линии задержки

Основная идея линий задержки возникла в ходе разработки радаров во время Второй мировой войны. В первых ЭВМ в качестве линий использовались трубки с ртутью (у нее очень низкое затухание ультразвуковых волн), на концах которой располагались передающий и принимающий пьезокристаллы. Информация подавалась с помощью импульсов, модулированных высокочастотным сигналом. Импульсы распространялись в ртути. Информационная емкость трубки в битах равнялась максимальному количеству одновременно передаваемых импульсов. Единица кодировалось присутствием импульса на определенном «месте», ноль — отсутствием импульса. Приемный пьезокристалл передавал импульс на передающий — информация циркулировала по кругу. Для записи вместо регенерации импульсов вводились записываемые. Такой вид памяти использовался в компьютерах EDVAC, EDSAC и UNIVAC I.

Запоминающее устройство на ртутных акустических линиях задержки в UNIVAC I

Запоминающие электронно-лучевые трубки (трубки Уильямса)

При попадании электронного луча на точку на люминофорном экране происходит вторичная эмиссия и участок люминофора приобретает положительный заряд. Благодаря сопротивлению люминофорного слоя, точка долю секунды держится на экране. Однако, если не отключать луч сразу, а сдвинуть его в сторону от точки, рисуя тире, то электроны, испущенные во время эмиссии, поглощаются точкой, и та приобретает нейтральный заряд. Таким образом, если выделить N точек, то можно записать N бит информации (1 — нейтральный заряд, 0 — положительный заряд). Для считывания информации используется доска с электродами, прикрепленная к внешней стороне экрана. Электронный луч снова направляется в точку, и та приобретает положительный заряд независимо от изначального. С помощью электрода можно определить величину изначального заряда (значение бита), однако информация уничтожается (после каждого считывания нужна перезапись). Так как люминофор быстро теряет заряд, необходимо постоянно считывать и записывать информацию. Такой вид памяти использовался в Манчестерском Марк I и Ferranti Mark1; американских IBM 701 и 702

Магнитные барабаны

Магнитные барабаны чем-то похожи на современные магнитные диски. На поверхность барабана был нанесен тонкий ферромагнитный слой. Несколько считывающих головок, расположенных по образующим диска, считывают и записывают данные на своей отдельной магнитной дорожке.

Архитектура фон Неймана

Архитектура фон Неймана строилась на следующих принципах:

Основным недостатком этой архитектуры является ограничение пропускной способности между памятью и процессором. Из-за того, что программа и данные не могут считываться одновременно, пропускная способность между памятью и процессором существенно ограничивает скорость работы процессора. В дальнейшем, данную проблему решили с помощью введения кеша, что вызвало другие проблемы( например, уязвимость Meltdown).

Справедливости ради необходимо уточнить, что данные идеи не являются идеями Джона фон Неймана в полной степени. Также в их разработке участвовали ещё несколько ученых, пионеров компьютерной техники: Джон Преспер Экерт и Джон Уильям Мокли.

Гарвардская архитектура

Языки

В самых первых компьютерах программы считывались с перфоленты (как в Z3 и Mark I). Устройство чтения перфоленты предоставляло управляющему устройство код операции для каждой инструкции и адреса памяти. Затем управляющее устройство все это декодировало, посылало управляющие сигналы вычислительному блоку и памяти. Набор инструкций жестко задавался в схеме, каждая машинная инструкция (сложение, сдвиг, копирование) реализовывалась непосредственно в схеме. В ENIAC для изменения программы его нужно было перекоммутировать заново, на что уходило значительное время. Машинные коды считают первым поколением языков программирования.

Перфорированная лента с программой вычислений

Первые программисты всегда имели при себе блокнот, в который они записывали наиболее употребляемые подпрограммы — независимые фрагменты программы, вызываемые из главной подпрограммы, например извлечение корня или вывод символа на дисплей. Проблема состояла в том, что адреса расположения переменных и команд менялись в зависимости от размещения в главной программе. Для решения этой проблемы кембриджские программисты разработали набор унифицированных подпрограмм (библиотеку), которая автоматически настраивали и размещали подпрограммы в памяти. Морис Уилкс, один из разработчиков EDSAC (первого практически реализованного компьютера с хранимой в памяти программой), назвал библиотеку подпрограмм собирающей системой (assembly system). Теперь не нужно было собирать программу вручную из машинных кодов, специальная программа (ассемблер) «автоматически» собирала программу. Первые ассемблеры спроектированы Кэтлин Бут в 1947 под ARC2 и Дэвидом Уилером в 1948 под EDSAC. При этом сам язык (мнемоники) называли просто множеством базовых команд или начальными командами. Использовать слово «ассемблер» для процесса объединения полей в командное слово начали в поздних отчетах по EDSAC. Ассемблер можно назвать вторым поколением языков.

«Начальные команды» для EDSAC

Компьютеры первого поколения в СССР

После Второй мировой войны часть немецких разработок в области компьютерных технологий перешли СССР. Ведущие специалисты сразу заинтересовались возможностями ЭВМ, а правительство согласилось, что устройства для быстрых и точных вычислений — это перспективное направление.

МЭСМ и БЭСМ

В 1948 году основоположник советской вычислительной техники С.А. Лебедев направил в Академию наук СССР докладную записку: в ней сообщалось о необходимости создания ЭВМ для практического использования и научного прогресса. Для разработки этой машины под Киевом, в Феофании институту отвели здание, ранее принадлежавшее монастырю. Через 2 года МЭСМ (малая электронная счетная машина) произвела первые вычисление — нахождение корней дифференциального уравнения. В 1951 году инспекция из академии наук приняла работу Лебедева. МЭСМ имела сложную трехадресную систему команд и следующие характеристики:

В 1950 году Лебедева перевели в Москву. Там он начал работать над БЭСМ-1 и к 1953 году построил опытный образец, отличавшийся отличной производительностью. Характеристики были следующими:

Серия «М» и «Стрела»

В тоже время в Москве велась работа над М-1. М-1 была намного менее мощной, чем МЭСМ, но при этом занимала намного меньше места и тратила меньше энергии. Характеристики М-1:

В 1952 году на свет выпустили М-2. Её мощность увеличилась практически в 100 раз, при этом количество ламп увеличилось только вдвое. Подобный результат получился благодаря использованию управляющих полупроводниковых диодов. Характеристики М-2 были следующие:

В «массовое» производство первой попала «Стрела». Всего было произведено 7 штук. Характеристики «Стрелы» были следующие:

Во многих смыслах «Стрела» была хуже М-2. Она выполняла всё те же 2 тысячи операций в секунду, но при этом занимала на порядок больше места и тратила в несколько раз больше электричества. М-2 не попала в массовое производство, поскольку её создатели не уложились в срок. М-1 не обладала хорошей производительностью и к моменту, когда М-2 была доведена до ума, «Стрела» была отдана в производство.

Следующий потомок серии «М» — М-3 вышел в 1956 году и был в каком-то смысле урезанным вариантом. Она выполняла порядка 30 операций в секунду, но при этом занимала мало места, благодаря чему пошла в серийное производство. Характеристики М-3 были следующие:

Эпилог

Без технологического рывка, сделанного в 40-е годы, и четко сформированного вектора развития вычислительной техники, возможно, сегодня мы бы и не сидели в компьютерах и телефонах, читая статейки на хабре. Как показал опыт разных ученых, порой уникальные и революционные для своего времени образцы вычислительной техники не были востребованы как государством, так и обществом (например, машины серии Z Конрада Цузе). Переход ко второму поколению компьютеров во многом определился сменой вакуумных ламп на транзисторы и изобретением накопителей на ферритовых сердечниках. Но это уже другая история…

Облачные серверы от Маклауд быстрые и надежные. Без древнего железа.

Зарегистрируйтесь по ссылке выше или кликнув на баннер и получите 10% скидку на первый месяц аренды сервера любой конфигурации!