Уровни детализации структуры вычислительной машины

Уровни детализации структуры вычислительной машины

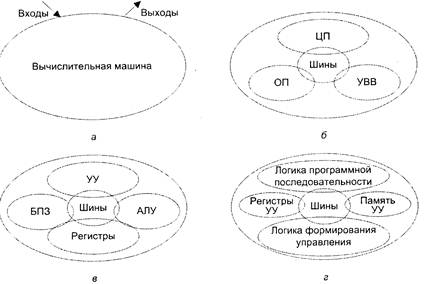

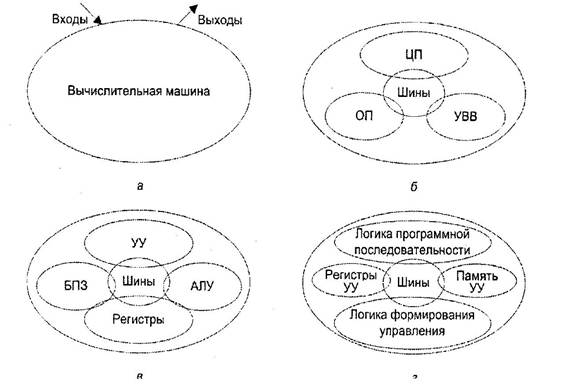

Рис. 1.1. Уровни детализации вычислительной машины:

а — уровень «черного ящика»;

б — уровень общей архитектуры;

в — уровень архитектуры центрального процессора;

г — уровень архитектуры устройства управления

На первом уровне вычислительная машина рассматривается как устройство, способное хранить и обрабатывать информацию, а также обмениваться данными с внешним миром (см. рис. 1.1, а). ВМ представляется «черным ящиком», который может быть подключен к коммуникационной сети и к которому, в свою очередь, могут подсоединяться периферийные устройства.

Уровень общей архитектуры (см. рис. 1.1,6) предполагает представление ВМ в виде четырех составляющих: центрального процессора (ЦП), основной памяти (ОП), устройства ввода/вывода (УВВ) и системы шин.

На третьем уровне детализируется каждое из устройств второго уровня. Для примера взят центральный процессор (см. рис. 1.1, в). В простейшем варианте в нем можно выделить:

арифметико-логическое устройство (АЛУ), обеспечивающее обработку целых чисел; блок обработки чисел в формате с плавающей запятой (БПЗ); регистры процессора, использующиеся для краткосрочного хранения команд, данных и адресов; устройство управления (УУ), обеспечивающее совместное функционирование устройств ВМ; внутренние шины.

На четвертом уровне детализируются элементы третьего уровня. Так, на рис. 1.1, г раскрыта структура устройства управления. УУ представлено в виде четырех составляющих: логики программной последовательности — электронных схем, обеспечивающих выполнение команд программы в последовательности, предписываемой программой; регистров и дешифраторов устройства управления; управляющей памяти; логики формирования управления, генерирующей все необходимые управляющие сигналы.

Применительно к параллельным и распределенным многопроцессорным и многомашинным вычислительным системам зачастую вводят понятие «метауровня».

Нам важно ваше мнение! Был ли полезен опубликованный материал? Да | Нет

Уровни детализации структуры вычислительной машины

Основные термины

ВВЕДЕНИЕ

РАЗДЕЛ 1

Вычислительная машина – это комплекс технических и программных средств, предназначенный для автоматизации подготовки и решения задач пользователей.

Вычислительная система – определим как совокупность взаимосвязанных и взаимодействующих процессоров или вычислительных машин, периферийного оборудования и программного обеспечения, предназначенную для подготовки и решения задач пользователей.

Таким образом, формально отличие вычислительной системы (ВС) от вычислительной машины (ВМ) выражается в количестве вычислителей. Множественность вычислителей позволяет реализовать в ВС параллельную обработку. С другой стороны, современные вычислительные машины с одним процессором также обладают определенными средствами распараллеливания вычислительного процесса. Иными словами, грань между ВМ и ВС часто бывает весьма расплывчатой, что дает основание там, где это целесообразно, рассматривать ВМ как одну из реализаций ВС. И напротив, вычислительные системы часто строятся из традиционных ВМ и процессоров, поэтому многие из положений, относящихся к ВМ, могут быть распространены и на ВС.

Архитектура вычислительной машины – логическое построение вычислительной машины, то есть то, какой машина представляется программисту. Подобную трактовку называют «узкой», и охватывает она перечень и формат команд, формы представления данных, механизмы ввода/вывода, способы адресации памяти и т. п. Из рассмотрения выпадают вопросы физического построения вычислительных средств: состав устройств, число регистров процессора, емкость памяти, наличие специального блока для обработки вещественных чисел, тактовая частота центрального процессора и т. д. Этот круг вопросов принято определять понятием организация или структурная организация.

Архитектура (в узком смысле) и организация – это две стороны описания и вычислительной системы. Применительно к вычислительным системам термин «архитектура» дополнительно распространяется на вопросы распределения функций между составляющими вычислительной системы и взаимодействия этих составляющих.

Вычислительная машина как законченный объект являет собой плод усилий специалистов в самых различных областях человеческих знаний. Каждый специалист рассматривает вычислительную машину с позиций стоящей перед ним задачи, абстрагируясь от несущественных, по его мнению, деталей.

В принципе таких уровней может быть достаточно много, однако сложившаяся практика ограничивает их число четырьмя уровнями (рис. 1.1)

Рис. 1.1. Уровни детализации вычислительной машины:

а) уровень «черного ящика»; б) уровень общей архитектуры;

в) уровень архитектуры центрального процессора;

г)уровень архитектуры устройства управления

На первом уровне вычислительная машина рассматривается как устройство, способное хранить и обрабатывать информацию, а также обмениваться данными с внешним миром (рис.1.1, а). ВМ представляется «черным ящиком», который может быть подключен к коммуникационной сети и к которому, в свою очередь, могут подсоединяться устройства.

Уровень общей архитектуры (рис. 1.1, б) представляет ВМ в виде четырех составляющих: центрального процессора (ЦП), основной памяти (ОП), устройства ввода/вывода (УВВ) и системы шин.

На третьем уровне детализируется каждое из второго уровня. Для взят центральный процессор (рис. 1.1, в). В простейшем в нем можно выделить:

• арифметико-логическое устройство (АЛУ); обеспечивающее обработку целых чисел;

• блок обработки чисел в формате с плавающей запятой (БПЗ);

• регистры процессора, использующиеся для краткосрочного хранения команд, данных и адресов;

• устройство управления (УУ), обеспечивающее совместное функционирование устройств ВМ;

На четвертом уровне детализируются элементы третьего уровня. Так, на рис.1.1, г раскрыта структура устройства управления. УУ представлено в виде четырех составляющих:

• логики программной последовательности – электронных схем, обеспечивающих выполнение команд программы в последовательности, предписываемой программой;

• регистров и дешифраторов устройства управления;

• логики формирования управления, генерирующей все необходимые управляющие сигналы.

Уровни детализации структуры вычислительной машины

Издание: Организация ЭВМ и систем: Учебник для вузов

Глава 1

Становление и эволюция цифровой вычислительной техники

Не отдавая предпочтения ни одной из известных формулировок терминов «вычислительная машина» и «вычислительная система», тем не менее воспользуемся наиболее общим их определением [33], условившись, что по мере необходимости смысловое их наполнение может уточняться.

Термином вычислительная машина будем обозначать комплекс технических и программных средств, предназначенный для автоматизации подготовки и решения задач пользователей.

В свою очередь, вычислительную систему определим как совокупность взаимосвязанных и взаимодействующих процессоров или вычислительных машин, периферийного оборудования и программного обеспечения, предназначенную для подготовки и решения задач пользователей.

Таким образом, формально отличие ВС от ВМ выражается в количестве вычислителей. Множественность вычислителей позволяет реализовать в ВС параллельную обработку. С другой стороны, современные вычислительные машины с одним процессором также обладают определенными средствами распараллеливания вычислительного процесса. Иными словами, грань между ВМ и ВС часто бывает весьма расплывчатой, что дает основание там, где это целесообразно, рассматривать ВМ как одну из реализаций ВС. И напротив, вычислительные системы часто строятся из традиционных ВМ и процессоров, поэтому многие из положений, относящихся к ВМ, могут быть распространены и на ВС. Последнее замечание имеет непосредственное отношение к материалу данной главы. Условимся, что сказанное относительно вычислительных машин распространяется и на ВС с традиционными процессорами. В тех случаях, когда излагаемый материал справедлив лишь по отношению ВС, структура или принцип действия которых отличается от традиционных, будет действовать термин «вычислительная система».

И, наконец, заключительное замечание. Специфика главы вынуждает использовать в ней многие понятия, полное содержание которых станет ясным лишь после изучения последующих разделов книги. Там, где это возможно, пояснения будут даваться по ходу изложения (правда, в упрощенном виде). В любом случае, для получения полной картины к материалу данной главы имеет смысл еще раз вернуться после ознакомления со всей книгой.

Определение понятия «архитектура»

Под архитектурой вычислительной машины обычно понимается логическое построение ВМ, то есть то, какой машина представляется программисту. Впервые термин «архитектура вычислительной машины» (computer architecture) был употреблен фирмой IBM при разработке машин семейства IBM 360 для описания тех средств, которыми может пользоваться программист, составляя программу на уровне машинных команд. Подобную трактовку называют «узкой», и охватывает она перечень и формат команд, формы представления данных, механизмы ввода/вывода, способы адресации памяти и т. п. Из рассмотрения выпадают вопросы физического построения вычислительных средств: состав устройств, число регистров процессора, емкость памяти, наличие специального блока для обработки вещественных чисел, тактовая частота центрального процессора и т. д. Этот круг вопросов принято определять понятием организация или структурная организация.

Архитектура (в узком смысле) и организация — это две стороны описания ВМ и ВС. Поскольку для наших целей, помимо теоретической строгости, такое деление не дает каких-либо преимуществ, то в дальнейшем будем пользоваться термином «архитектура», правда, в «широком» его толковании, объединяющем как архитектуру в узком смысле, так и организацию ВМ. Применительно к вычислительным системам термин «архитектура» дополнительно распространяется на вопросы распределения функций между составляющими ВС и взаимодействия этих составляющих.

Уровни детализации структуры вычислительной машины

Таблица 1.1. Распределение функций между разработчиками вычислительной машины

| Специалист | Круг вопросов |

| Производитель полупроводниковых материалов | Материал для интегральных микросхем (легированный кремний, диоксид кремния и т. п.) |

| Разработчик электронных схем | Электронные схемы узлов ВМ (разработка и анализ) |

| Разработчик интегральных микросхем | Сверхбольшие интегральные микросхемы (схемы электронных элементов, их размещение на кристалле) |

| Системный архитектор | Архитектура и организация вычислительной машины (устройства и узлы, система команд и т. п.) |

| Системный программист | Операционная система, компиляторы |

| Теоретик | Алгоритмы, абстрактные структуры данных |

Круг вопросов, рассматриваемых в данном курсе, по большей части относится к компетенции системного архитектора и охватывает различные степени детализации ВМ и ВС. В принципе таких уровней может быть достаточно много, однако сложившаяся практика ограничивает их число четырьмя уровнями (рис. 1.1).

Рис. 1.1. Уровни детализации вычислительной машины: а — уровень «черного ящика»;

б — уровень общей архитектуры; в — уровень архитектуры центрального процессора;

г — уровень архитектуры устройства управления

На первом уровне вычислительная машина рассматривается как устройство, способное хранить и обрабатывать информацию, а также обмениваться данными с внешним миром (см. рис. 1.1, а). ВМ представляется «черным ящиком», который может быть подключен к коммуникационной сети и к которому, в свою очередь, могут подсоединяться периферийные устройства.

Уровень общей архитектуры (см. рис. 1.1, б) предполагает представление ВМ в виде четырех составляющих: центрального процессора (ЦП), основной памяти (ОП), устройства ввода/вывода (УВВ) и системы шин.

Применительно к параллельным и распределенным многопроцессорным и многомашинным вычислительным системам зачастую вводят понятие «метауровня». На данном этапе метауровень рассматриваться не будет.

Эволюция средств автоматизации вычислений

По мнению специалистов в области теории эволюции компьютеров, изучение закономерностей развития вычислительных машин и систем может, как и в биологии, привести к ощутимым практическим результатам.

При описании эволюции ВТ обычно используют один из двух подходов: хронологический или технологический. В первом случае — это хронология событий, существенно повлиявших на становление ВТ. Для наших целей больший интерес представляет технологический подход, когда развитие вычислительной техники рассматривается в терминах архитектурных решений и технологий. По словам главного конструктора фирмы DEC и одного из изобретателей мини-ЭВМ Белла: — «История компьютерной индустрии почти всегда двигалась технологией».

Значительно большее распространение, однако, получила привязка поколений к смене технологий. Принято говорить о «механической» эре (нулевое поколение) и последовавших за ней пяти поколениях ВС [210]. Первые четыре поколения традиционно связывают с элементной базой вычислительных систем: электронные лампы, полупроводниковые приборы, интегральные схемы малой степени интеграции (ИМС), большие (БИС), сверхбольшие (СБИС) и ультрабольшие (УБИС) интегральные микросхемы. Пятое поколение в общепринятой интерпретации ассоциируют не столько с новой элементной базой, сколько с интеллектуальными возможностями ВС. Работы по созданию ВС пятого поколения велись в рамках четырех достаточно независимых программ, осуществлявшихся учеными США, Японии, стран Западной Европы и стран Совета экономической взаимопомощи. Ввиду того, что ни одна из программ не привела к ожидаемым результатам, разговоры о ВС пятого поколения понемногу утихают. Трактовка пятого поколения явно выпадает из «технологического» принципа. С другой стороны, причисление всех ВС на базе сверхбольших интегральных схем (СБИС) к четвертому поколению не отражает принципиальных изменений в архитектуре ВС, произошедших за последние годы. Чтобы в какой-то мере проследить роль таких изменений, воспользуемся несколько отличной трактовкой, предлагаемой в [174]. В работе выделяется шесть поколений ВС. Попытаемся кратко охарактеризовать каждое из них, выделяя наиболее значимые события.

Нулевое поколение (1492–1945)

«Механическая» эра (нулевое поколение) в эволюции ВТ связана с механическими, а позже — электромеханическими вычислительными устройствами. Основным элементом механических устройств было зубчатое колесо. Начиная с XX века роль базового элемента переходит к электромеханическому реле. Не умаляя значения многих идей «механической» эры, необходимо отметить, что ни одно из созданных устройств нельзя с полным основанием назвать вычислительной машиной в современном ее понимании. Чтобы подчеркнуть это, вместо термина «вычислительная машина» будем использовать такие слова, как «вычислитель», «калькулятор» и т. п.

Хронология основных событий «механической» эры выглядит следующим образом.

1492 год. В одном из своих дневников Леонардо да Винчи приводит рисунок тринадцатиразрядного десятичного суммирующего устройства на основе зубчатых колес.

1623 год. Вильгельм Шиккард (Wilhelm Schickard, 1592–1635), профессор университета Тюбингена, разрабатывает устройство на основе зубчатых колес («считающие часы») для сложения и вычитания шестиразрядных десятичных чисел. Было ли устройство реализовано при жизни изобретателя, достоверно неизвестно, но в 1960 году оно было воссоздано и проявило себя вполне работоспособным.

1642 год. Блез Паскаль (Blaise Pascal, 1623–1663) представляет «Паскалин» — первое реально осуществленное и получившее известность механическое цифровое вычислительное устройство. Прототип устройства суммировал и вычитал пятиразрядные десятичные числа. Паскаль изготовил более десяти таких вычислителей, причем последние модели оперировали числами длиной в восемь цифр.

1673 год. Готфрид Вильгельм Лейбниц (Gottfried Wilhelm Leibniz, 1646–1716) создает «пошаговый вычислитель» — десятичное устройство для выполнения всех четырех арифметических операций над 12-разрядными десятичными числами. Результат умножения представлялся 16 цифрами. Помимо зубчатых колес в устройстве использовался новый элемент — ступенчатый валик.

1786 год. Немецкий военный инженер Иоганн Мюллер (Johann Mueller, 1746–1830) выдвигает идею «разностной машины» — специализированного калькулятора для табулирования логарифмов, вычисляемых разностным методом. Калькулятор, построенный на ступенчатых валиках Лейбница, получился достаточно небольшим (13 см в высоту и 30 см в диаметре), но при этом мог выполнять все четыре арифметических действия над 14-разрядными числами.

1801 год. Жозеф Мария Жаккард (Joseph-Marie Jacquard, 1752–1834) строит ткацкий станок с программным управлением, программа работы которого задается с помощью комплекта перфокарт.

1832 год. Английский математик Чарльз Бэббидж (Charles Babbage, 1792–1871) создает сегмент разностной машины, оперирующий шестиразрядными числами и разностями второго порядка. Разностная машина Бэббиджа по идее аналогична калькулятору Мюллера.

1834 год. Пер Георг Шутц (Per George Scheutz, 1785–1873) из Стокгольма, используя краткое описание проекта Бэббиджа, создает из дерева небольшую разностную машину.

1836 год. Бэббидж разрабатывает проект «аналитической машины». Проект предусматривает три считывателя с перфокарт для ввода программ и данных, память (по Бэббиджу — «склад») на пятьдесят 40-разрядных чисел, два аккумулятора для хранения промежуточных результатов. В программировании машины предусмотрена концепция условного перехода. В проект заложен также и прообраз микропрограммирования — содержание инструкций предполагалось задавать путем позиционирования металлических штырей в цилиндре с отверстиями. По оценкам автора, суммирование должно было занимать 3 с, а умножение и деление — 2–4 мин.

1843 год. Георг Шутц совместно с сыном Эдвардом (Edvard Scheutz, 1821–1881) строят разностную машину с принтером для работы с разностями третьего порядка.

1871 год. Бэббидж создает прототип одного из устройств своей аналитической машины — «мельницу» (так он окрестил то, что сейчас принято называть центральным процессором), а также принтер.

1885 год. Дорр Фельт (Dorr E. Felt, 1862–1930) из Чикаго строит свой «комптометр» — первый калькулятор, где числа вводятся нажатием клавиш.

1890 год. Результаты переписи населения в США обрабатываются с помощью перфокарточного табулятора, созданного Германом Холлеритом (Herman Hollerith, 1860–1929) из Массачусетсского технологического института.

1892 год. Вильям Барроуз (William S. Burroughs, 1857–1898) предлагает устройство, схожее с калькулятором Фельта, но более надежное, и от этого события берет старт индустрия офисных калькуляторов.

1937 год. Джорж Стибитц (George Stibitz, 1904–1995) из Bell Telephone Laboratories демонстрирует первый однобитовый двоичный вычислитель на базе электромеханических реле.

1937 год. Алан Тьюринг (Alan M. Turing, 1912–1954) из Кембриджского университета публикует статью, в которой излагает концепцию теоретической упрощенной вычислительной машины, в дальнейшем получившей название машины Тьюринга.

1938 год. Клод Шеннон (Claude E. Shannon, 1916–2001) публикует статью о реализации символической логики на базе реле.

1938 год. Немецкий инженер Конрад Цузе (Konrad Zuse, 1910–1995) строит механический программируемый вычислитель Z1 с памятью на 1000 бит. В последнее время Z1 все чаще называют первым в мире компьютером.

1939 год. Джордж Стибитц и Сэмюэль Вильямс (Samuel Williams, 1911–1977) представили Model I — калькулятор на базе релейной логики, управляемый с помощью модифицированного телетайпа, что позволило подключаться к калькулятору по телефонной линии. Более поздние модификации допускали также определенную степень программирования.

1940 год. Следующая работа Цузе — электромеханическая машина Z2, основу которой составляла релейная логика, хотя память, как и в Z1, была механической.

1941 год. Цузе создает электромеханический программируемый вычислитель Z3. Вычислитель содержит 2600 электромеханических реле. Z3 — это первая попытка реализации принципа программного управления, хотя и не в полном объеме (в общепринятом понимании этот принцип еще не был сформулирован). В частности, не предусматривалась возможность условного перехода. Программа хранилась на перфоленте. Емкость памяти составляла 64 22-битовых слова. Операция умножения занимала 3–5 с.

1943 год. Группа ученых Гарвардского университета во главе с Говардом Айкеном (Howard Aiken, 1900–1973) разрабатывает вычислитель ASCC Mark I (Automatic Sequence-Controlled Calculator Mark I) — первый программно управляемый вычислитель, получивший широкую известность. Длина устройства составила 18 м, а весило оно 5 т. Машина состояла из множества вычислителей, обрабатывающих свои части общей задачи под управлением единого устройства управления. Команды считывались с бумажной перфоленты и выполнялись в порядке считывания. Данные считывались с перфокарт. Вычислитель обрабатывал 23-разрядные числа, при этом сложение занимало 0,3 с, умножение — 4 с, а деление — 10 с.

1945 год. Цузе завершает Z4 — улучшенную версию вычислителя Z3. По архитектуре у Z4 очень много общих черт с современными ВМ: память и процессор представлены отдельными устройствами, процессор может обрабатывать числа с плавающей запятой и, в дополнение к четырем основным арифметическим операциям, способен извлекать квадратный корень. Программа хранится на перфоленте и считывается последовательно.

Не умаляя важности каждого из перечисленных фактов, в качестве важнейшего момента «механической» эпохи все-таки выделим аналитическую машину Чарльза Бэббиджа и связанные с ней идеи.

Первое поколение (1937–1953)

Первой электронной вычислительной машиной чаще всего называют специализированный калькулятор ABC (Atanasoff–Berry Computer). Разработан он был в период с 1939 по 1942 год профессором Джоном Атанасовым (John V. Atanasoff, 1903–1995) совместно с аспирантом Клиффордом Берри (Clifford Berry, 1918–1963) и предназначался для решения системы линейных уравнений (до 29 уравнений с 29 переменными). ABC обладал памятью на 50 слов длиной 50 бит, а запоминающими элементами служили конденсаторы с цепями регенерации. В качестве вторичной памяти использовались перфокарты, где отверстия не перфорировались, а прожигались. ABC стал считаться первой электронной ВМ, после того как судебным решением были аннулированы патенты создателей другого электронного калькулятора — ENIAC. Необходимо все же отметить, что ни ABC, ни ENIAC не являются вычислительным машинами в современном понимании этого термина и их правильней классифицировать как калькуляторы.

Вторым претендентом на первенство считается вычислитель Colossus, построенный в 1943 году в Англии в местечке Bletchley Park близ Кембриджа. Изобретателем машины был профессор Макс Ньюмен (Max Newman, 1987–1984), а изготовил его Томми Флауэрс (Tommy Flowers, 1905–1998). Colossus был создан для расшифровки кодов немецкой шифровальной машины «Лоренц Шлюссель-цузат-40». В состав команды разработчиков входил также Алан Тьюринг. Машина была выполнена в виде восьми стоек высотой 2,3 м, а общая длина ее составляла 5,5 м. В логических схемах машины и в системе оптического считывания информации использовалось 2400 электронных ламп, главным образом тиратронов. Информация считывалась с пяти вращающихся длинных бумажных колец со скоростью 5000 символов/с.

При всей важности каждой из трех рассмотренных разработок основное событие, произошедшее в этот период, связано с именем Джона фон Неймана. Американский математик Джон фон Нейман (John von Neumann, 1903–1957) принял участие в проекте ENIAC в качестве консультанта. Еще до завершения ENIAC Эккерт, Мочли и фон Нейман приступили к новому проекту — EDVAC, главной особенностью которого стала идея хранимой в памяти программы.

Технология программирования в рассматриваемый период была еще на зачаточном уровне. Первые программы составлялись в машинных кодах — числах, непосредственно записываемых в память ВМ. Лишь в 50-х годах началось использование языка ассемблера, позволявшего вместо числовой записи команд использовать символьную их нотацию, после чего специальной программой, также называемой ассемблером, эти символьные обозначения транслировались в соответствующие коды.

Несмотря на свою примитивность, машины первого поколения оказались весьма полезными для инженерных целей и в прикладных науках. Так, Атанасофф подсчитал, что решение системы из восьми уравнений с восемью переменными с помощью популярного тогда электромеханического калькулятора Маршана заняло бы восемь часов. В случае же 29 уравнений с 29 переменными, с которыми калькулятор ABC справлялся менее чем за час, устройство с калькулятором Маршана затратило бы 381 час. С первой задачей в рамках проекта водородной бомбы ENIAC справился за 20 с, в противовес 40 часам, которые понадобились бы при использовании механических калькуляторов.

В 1947 году под руководством С. А. Лебедева начаты работы по созданию малой электронной счетной машины (МЭСМ). Эта ВМ была запущена в эксплуатацию в 1951 году и стала первой электронной ВМ в СССЗ и континентальной Европе.

В 1952 году Эккерт и Мочли создали первую коммерчески успешную машину UNIVAC. Именно с помощью этой ВМ было предсказано, что Эйзенхауэр в результате президентских выборов победит Стивенсона с разрывом в 438 голосов (фактический разрыв составил 442 голоса).

Также в 1952 году в опытную эксплуатацию была запущена вычислительная машина М-1 (И. С. Брук, Н. Я. Матюхин, А. Б. Залкинд). М-1 содержала 730 электронных ламп, оперативную память емкостью 256 25-разрядных слов, рулонный телетайп и обладала производительностью 15–20 операций/с. Впервые была применена двухадресная система команд. Чуть позже группой выпускников МЭИ под руководством И. С. Брука создана машина М-2 с емкостью оперативной памяти 512 34-разрядных слов и быстродействием 2000 операций/с.

В апреле 1953 года в эксплуатацию поступила самая быстродействующая в Европе ВМ БЭСМ (С. А. Лебедев). Ее быстродействие составило 8000–10 000 операций/с. Примерно в то же время выпущена ламповая ВМ «Стрела» (Ю. А. Базилевский, Б. И. Рамееев) с быстродействием 2000 операций/с.

Второе поколение (1954–1962)

Первой ВМ, выполненной полностью на полупроводниковых диодах и транзисторах, стала TRADIC (TRAnisitor DIgital Computer), построенная в Bell Labs по заказу военно-воздушных сил США как прототип бортовой ВМ. Машина состояла из 700 транзисторов и 10 000 германиевых диодов. За два года эксплуатации TRADIC отказали только 17 полупроводниковых элементов, что говорит о прорыве в области надежности, по сравнению с машинами на электронных лампах. Другой достойной упоминания полностью полупроводниковой ВМ стала TX-0, созданная в 1957 году в Массачусетсском технологическом институте.

Со вторым поколением ВМ ассоциируют еще одно принципиальное технологическое усовершенствование — переход от устройств памяти на базе ртутных линий задержки к устройствам на магнитных сердечниках. В запоминающих устройствах (ЗУ) на линиях задержки данные хранились в виде акустической волны, непрерывно циркулирующей по кольцу из линий задержки, а доступ к элементу данных становился возможным лишь в момент прохождения соответствующего участка волны вблизи устройства считывания/записи. Главным преимуществом ЗУ на магнитных сердечниках стал произвольный доступ к данным, когда в любой момент доступен любой элемент данных, причем время доступа не зависит от того, какой это элемент.

Технологический прогресс дополняют важные изменения в архитектуре ВМ. Прежде всего, это касается появления в составе процессора ВМ индексных регистров, что позволило упростить доступ к элементам массивов. Прежде, при циклической обработке элементов массива, необходимо было модифицировать код команды, в частности хранящийся в нем адрес элемента массива. Как следствие, в ходе вычислений коды некоторых команд постоянно изменялись, что затрудняло отладку программы. С использованием индексных регистров адрес элемента массива вычисляется как сумма адресной части команды и содержимого индексного регистра. Это позволяет обратиться к любому элементу массива, не затрагивая код команды, а лишь модифицируя содержимое индексного регистра.

Вторым принципиальным изменением в структуре ВМ стало добавление аппаратного блока обработки чисел в формате с плавающей запятой. До этого обработка вещественных чисел производилась с помощью подпрограмм, каждая из которых имитировала выполнение какой-то одной операции с плавающей запятой (сложение, умножение и т. п.), используя для этой цели обычное целочисленное арифметико-логическое устройство.

Третье значимое нововведение в архитектуре ВМ — появление в составе вычислительной машины процессоров ввода/вывода, позволяющих освободить центральный процессор от рутинных операций по управлению вводом/выводом и обеспечивающих более высокую пропускную способность тракта «память — устройства ввода/вывода» (УВВ).

Ко второму поколению относятся и две первые суперЭВМ, разработанные для ускорения численных вычислений в научных приложениях. Термин «суперЭВМ» первоначально применялся по отношению к ВМ, производительность которых на один или более порядков превосходила таковую для прочих вычислительных машин того же поколения. Во втором поколении этому определению отвечали две ВМ (правильнее сказать системы): LARC (Livermore Atomic Research Computer) и IBM 7030. Помимо прочего, в этих ВМ нашли воплощение еще две новинки: совмещение операций процессора с обращением к памяти и простейшие формы параллельной обработки данных.

Заметным событием данного периода стало появление в 1958 году машины М-20. В этой ВМ, в частности, были реализованы: частичное совмещение операций, аппаратные средства поддержки программных циклов, возможность параллельной работы процессора и устройства вывода. Оперативная память емкостью 4096 45 разрядных слов была выполнена на магнитных сердечниках.

Шестидесятые годы XX века стали периодом бурного развития вычислительной техники в СССР. За этот период разработаны и запущены в производство вычислительные машины «Урал-1», «Урал-4», «Урал-11», «Урал-14», БЭСМ-2, М-40, «Минск-1», «Минск-2», «Минск-22», «Минск-32». В 1960 году под руководством В. М. Глушкова и Б. Н. Малиновского разработана первая полупроводниковая управляющая машина «Днепр».

Наконец, нельзя не отметить значительные события в сфере программного обеспечения, а именно создание языков программирования высокого уровня: Фортрана (1956), Алгола (1958) и Кобола (1959).

Третье поколение (1963–1972)

В первых ВМ третьего поколения использовались интегральные схемы с малой степенью интеграции (small-scale integrated circuits, SSI), где на одном кристалле размещается порядка 10 транзисторов. Ближе к концу рассматриваемого периода на смену SSI стали приходить интегральные схемы средней степени интеграции (medium-scale integrated circuits, MSI), в которых число транзисторов на кристалле увеличилось на порядок. К этому же времени относится повсеместное применение многослойных печатных плат. Все шире востребуются преимущества параллельной обработки, реализуемые за счет множественных функциональных блоков, совмещения во времени работы центрального процессора и операций ввода/вывода, конвейеризации потоков команд и данных.

В 1964 году Сеймур Крей (Seymour Cray, 1925–1996) построил вычислительную систему CDC 6600, в архитектуру которой впервые был заложен функциональный параллелизм. Благодаря наличию 10 независимых функциональных блоков, способных работать параллельно, и 32 независимых модулей памяти удалось достичь быстродействия в 1 MFLOPS (миллион операций с плавающей запятой в секунду). Пятью годами позже Крей создал CDC 7600 с конвейеризированными функциональными блоками и быстродействием 10 MFLOPS. CDC 7600 называют первой конвейерной вычислительной системой (конвейерным процессором). Революционной вехой в истории ВТ стало создание семейства вычислительных машин IBM 360, архитектура и программное обеспечение которых на долгие годы служили эталоном для последующих больших универсальных ВМ (mainframes). В машинах этого семейства нашли воплощение многие новые для того периода идеи, в частности: предварительная выборка команд, отдельные блоки для операций с фиксированной и плавающей запятой, конвейеризация команд, кэш-память. К третьему поколению ВС относятся также первые параллельные вычислительные системы: SOLOMON корпорации Westinghause и ILLIAC IV — совместная разработка Иллинойского университета и компании Burroughs. Третье поколение ВТ ознаменовалось также появлением первых конвейерно-векторных ВС: TI-ASC (Texas Instruments Advanced Scientific Computer) и STAR-100 фирмы СВС.

Среди вычислительных машин, разработанных в этот период в СССР, прежде всего необходимо отметить «быстродействующую электронно-счетную машину» — БЭСМ-6 (С. А. Лебедев) с производительностью 1 млн операций/с. Продолжением линии М-20 стали М-220 и М-222 с производительностью до 200 000 операций/с. Оригинальная ВМ для инженерных расчетов «Мир-1» была создана под руководством В. М. Глушкова. В качестве входного языка этой ВМ использован язык программирования высокого уровня «Аналитик», во многом напоминающий язык Алгол.

В сфере программного обеспечения необходимо отметить создание в 1970 году Кеном Томпсоном (Kenneth Thompson) из Bell Labs языка B, прямого предшественника популярного языка программирования С, и появление ранней версии операционной системы UNIX.

Четвертое поколение (1972–1984)

Конец 70-х и начало 80-х годов — это время становления и последующего победного шествия микропроцессоров и микроЭВМ, что, однако, не снижает важности изменений, произошедших в архитектуре других типов вычислительных машин и систем.

Одним из наиболее значимых событий в области архитектуры ВМ стала идея вычислительной машины с сокращенным набором команд (RISC, Redused Instruction Set Computer), выдвинутая в 1975 году и впервые реализованная в 1980 году. В упрощенном изложении суть концепция RISC заключается в сведении набора команд ВМ к наиболее употребительным простейшим командам. Это позволяет упростить схемотехнику процессора и добиться резкого сокращения времени выполнения каждой из «простых» команд. Более сложные команды реализуются как подпрограммы, составленные из быстрых «простых» команд.

В ВМ и ВС четвертого поколения практически уходят со сцены ЗУ на магнитных сердечниках и основная память строится из полупроводниковых запоминающих устройств (ЗУ). До этого использование полупроводниковых ЗУ ограничивалось лишь регистрами и кэш-памятью.

В сфере высокопроизводительных вычислений доминируют векторные вычислительные системы, более известные как суперЭВМ. Разрабатываются новые параллельные архитектуры, однако подобные работы пока еще носят экспериментальный характер. На замену большим ВМ, работающим в режиме разделения времени, приходят индивидуальные микроЭВМ и рабочие станции (этим термином обозначают сетевой компьютер, использующий ресурсы сервера).

В области программного обеспечения выделим появление языков программирования сверхвысокого уровня, таких как FP (functional programming — функциональное программирование) и Пролог (Prolog, programming in logic). Эти языки ориентированы на декларативный стиль программирования, в отличие от Паскаля, С, Фортрана и т. д. — языков императивного стиля программирования. При декларативном стиле программист дает математическое описание того, что должно быть вычислено, а детали того, каким образом это должно быть сделано, возлагаются на компилятор и операционную систему. Такие языки пока используются недостаточно широко, но выглядят многообещающими для ВС с массовым параллелизмом, состоящими из более чем 1000 процессоров. В компиляторах для ВС четвертого поколения начинают применяться сложные методы оптимизации кода.

Два события в области программного обеспечения связаны с Кеном Томпсоном (Kenneth Thompson) и Деннисом Ритчи (Dennis Ritchie) из Bell Labs. Это создание языка программирования C и его использование при написании операционной системы UNIX для машины DEC PDP-11. Такая форма написания операционной системы позволила быстро распространить UNIX на многие ВМ.

Пятое поколение (1984–1990)

В рамках пятого поколения в архитектуре вычислительных систем сформировались два принципиально различных подхода: архитектура с совместно используемой памятью и архитектура с распределенной памятью.

Характерным примером первого подхода может служить система Sequent Balance 8000, в которой имеется большая основная память, разделяемая 20 процессорами. Помимо этого, каждый процессор оснащен собственной кэш-памятью. Каждый из процессоров может выполнять задачу своего пользователя, но при этом в составе программного обеспечения имеется библиотека подпрограмм, позволяющая программисту привлекать для решения своей задачи более одного процессора. Система широко использовалась для исследования параллельных алгоритмов и техники программирования.

Второе направление развития систем пятого поколения — системы с распределенной памятью, где каждый процессор обладает своим модулем памяти, а связь между процессорами обеспечивается сетью взаимосвязей. Примером такой ВС может служить система iPSC-1 фирмы Intel, более известная как «гиперкуб». Максимальный вариант системы включал 128 процессоров. Применение распределенной памяти позволило устранить ограничения в пропускной способности тракта «процессор-память», но потенциальным «узким местом» здесь становится сеть взаимосвязей.

Наконец, третье направление в архитектуре вычислительных систем пятого поколения — это ВС, в которых несколько тысяч достаточно простых процессоров работают под управлением единого устройства управления и одновременно производят одну и ту же операцию, но каждый над своими данными. К этому классу можно отнести Connection Machine фирмы Thinking Machines Inc. и MP-1 фирмы MasPar Inc.

В научных вычислениях по-прежнему ведущую роль играют векторные суперЭВМ. Многие производители предлагают более эффективные варианты с несколькими векторными процессорами, но число таких процессоров обычно невелико (от 2 до 8).

RISC-архитектура выходит из стадии экспериментов и становится базовой архитектурой для рабочих станций (workstations).

Знаковой приметой рассматриваемого периода стало стремительное развитие технологий глобальных и локальных компьютерных сетей. Это стимулировало изменения в технологии работы индивидуальных пользователей. В противовес мощным универсальным ВС, работающим в режиме разделения времени, пользователи все более отдают предпочтение подключенным к сети индивидуальным рабочим станциям. Такой подход позволяет для решения небольших задач задействовать индивидуальную машину, а при необходимости в большой вычислительной мощности обратиться к ресурсам подсоединенных к той же сети мощных файл-серверов или суперЭВМ.

Шестое поколение (1990–)

Поводом для начала отсчета нового поколения стали значительные успехи в области параллельных вычислений, связанные с широким распространением вычислительных систем с массовым параллелизмом. Особенности организации таких систем, обозначаемых аббревиатурой MPP (massively parallel processing), будут рассмотрены в последующих разделах. Здесь же упрощенно определим их как совокупность большого количества (до нескольких тысяч) взаимодействующих, но достаточно автономных вычислительных машин. По вычислительной мощности такие системы уже успешно конкурируют с суперЭВМ, которые, как ранее отмечалось, по своей сути являются векторными ВС. Появление вычислительных систем с массовым параллелизмом дало основание говорить о производительности, измеряемой в TFLOPS (1 TFLOPS соответствует 1012 операциям с плавающей запятой в секунду).

Вторая характерная черта шестого поколения — резко возросший уровень рабочих станций. В процессорах новых рабочих станций успешно совмещаются RISC-архитектура, конвейеризация и параллельная обработка. Некоторые рабочие станции по производительности сопоставимы с суперЭВМ четвертого поколения. Впечатляющие характеристики рабочих станций породили интерес к гетерогенным (неоднородным) вычислениям, когда программа, запущенная на одной рабочей станции, может найти в локальной сети не занятые в данный момент другие станции, после чего вычисления распараллеливаются и на эти простаивающие станции.

Наконец, третьей приметой шестого поколения в эволюции ВТ стал взрывной рост глобальных сетей. Этот момент, однако, выходит за рамки данной книги, поэтому далее комментироваться не будет.

Завершая обсуждение эволюции ВТ, отметим, что верхняя граница шестого поколения хронологически пока не определена и дальнейшее развитие вычислительной техники может внести в его характеристику новые коррективы. Не исключено также, что последующие события дадут повод говорить и об очередном поколении.

Концепция машины с хранимой в памяти программой

Основными свойствами алгоритма являются: дискретность, определенность, массовость и результативность.

Дискретность выражается в том, что алгоритм описывает действия над дискретной информацией (например, числовой или символьной), причем сами эти действия также дискретны.

Свойство определенности означает, что в алгоритме указано все, что должно быть сделано, причем ни одно из действий не должно трактоваться двояко.

Массовость алгоритма подразумевает его применимость к множеству значений исходных данных, а не только к каким-то уникальным значениям.

Наконец, результативность алгоритма состоит в возможности получения результата за конечное число шагов.

Рассмотренные свойства алгоритмов предопределяют возможность их реализации на ВМ, при этом процесс, порождаемый алгоритмом, называют вычислительным процессом.

В основе архитектуры современных ВМ лежит представление алгоритма решения задачи в виде программы последовательных вычислений. Согласно стандарту ISO 2382/1-84, программа для ВМ — это «упорядоченная последовательность команд, подлежащая обработке».

ВМ, где определенным образом закодированные команды программы хранятся в памяти, известна под названием вычислительной машины с хранимой в памяти программой. Идея принадлежит создателям вычислителя ENIAC Эккерту, Мочли и фон Нейману. Еще до завершения работ над ENIAC они приступили к новому проекту — EDVAC, главной особенностью которого стала концепция хранимой в памяти программы, на долгие годы определившая базовые принципы построения последующих поколений вычислительных машин. Относительно авторства существует несколько версий, но поскольку в законченном виде идея впервые была изложена в 1945 году в статье фон Неймана [219], именно его фамилия фигурирует в обозначении архитектуры подобных машин, составляющих подавляющую часть современного парка ВМ и ВС.

Принцип двоичного кодирования

Рис. 1.2. Структура команды

Код операции представляет собой указание, какая операция должна быть выполнена, и задается с помощью r-разрядной двоичной комбинации.

Вид адресной части и число составляющих ее адресов зависят от типа команды: в командах преобразования данных АЧ содержит адреса объектов обработки (операндов) и результата; в командах изменения порядка вычислений — адрес следующей команды программы; в командах ввода/вывода — номер устройства ввода/вывода. Адресная часть также представляется двоичной последовательностью, длину которой обозначим через p. Таким образом, команда в вычислительной машине имеет вид (r + p)-разрядной двоичной комбинации.

Принцип программного управления

Принцип однородности памяти

Концепция вычислительной машины, изложенная в статье фон Неймана, предполагает единую память для хранения команд и данных. Такой подход был принят в вычислительных машинах, создававшихся в Принстонском университете, из-за чего и получил название принстонской архитектуры. Практически одновременно в Гарвардском университете предложили иную модель, в которой ВМ имела отдельную память команд и отдельную память данных. Этот вид архитектуры называют гарвардской архитектурой. Долгие годы преобладающей была и остается принстонская архитектура, хотя она порождает проблемы пропускной способности тракта «процессор-память». В последнее время в связи с широким использованием кэш-памяти разработчики ВМ все чаще обращаются к гарвардской архитектуре.

Принцип адресности

Фон-неймановская архитектура

Рис. 1.3. Структура фон-неймановской вычислительной машины

В любой ВМ имеются средства для ввода программ и данных к ним. Информация поступает из подсоединенных к ЭВМ периферийных устройств (ПУ) ввода. Результаты вычислений выводятся на периферийные устройства вывода. Связь и взаимодействие ВМ и ПУ обеспечивают порты ввода и порты вывода. Термином порт обозначают аппаратуру сопряжения периферийного устройства с ВМ и управления им. Совокупность портов ввода и вывода называют устройством ввода/вывода (УВВ) или модулем ввода/вывода ВМ (МВВ).

Введенная информация сначала запоминается в основной памяти, а затем переносится во вторичную память, для длительного хранения. Чтобы программа могла выполняться, команды и данные должны располагаться в основной памяти (ОП), организованной таким образом, что каждое двоичное слово хранится в отдельной ячейке, идентифицируемой адресом, причем соседние ячейки памяти имеют следующие по порядку адреса. Доступ к любым ячейкам запоминающего устройства (ЗУ) основной памяти может производиться в произвольной последовательности. Такой вид памяти известен как память с произвольным доступом. ОП современных ВМ в основном состоит из полупроводниковых оперативных запоминающих устройств (ОЗУ), обеспечивающих как считывание, так и запись информации. Для таких ЗУ характерна энергозависимость — хранимая информация теряется при отключении электропитания. Если необходимо, чтобы часть основной памяти была энергонезависимой, в состав ОП включают постоянные запоминающие устройства (ПЗУ), также обеспечивающие произвольный доступ. Хранящаяся в ПЗУ информация может только считываться (но не записываться).

Размер ячейки основной памяти обычно принимается равным 8 двоичным разрядам — байту. Для хранения больших чисел используются 2, 4 или 8 байтов, размещаемых в ячейках с последовательными адресами. В этом случае за адрес числа часто принимается адрес его младшего байта. Так, при хранении 32-разрядного числа в ячейках с адресами 200, 201, 202 и 203 адресом числа будет 200. Такой прием называют адресацией по младшему байту или методом «остроконечников» (little endian addressing). Возможен и противоположный подход — по меньшему из адресов располагается старший байт. Этот способ известен как адресация по старшему байту или метод «тупоконечников» (big endian addressing)1. Адресация по младшему байту характерна для микропроцессоров фирмы Intel и мини-ЭВМ фирмы DEC, а по старшему байту — для микропроцессоров фирмы Motorola и универсальных ЭВМ фирмы IBM. В принципе выбор порядка записи байтов существенен лишь при пересылке данных между ВМ с различными формами их адресации или при манипуляциях с отдельными байтами числа. В большинстве ВМ предусмотрены специальные инструкции для перехода от одного способа к другому.

Для долговременного хранения больших программ и массивов данных в ВМ обычно имеется дополнительная память, известная как вторичная. Вторичная память энергонезависима и чаще всего реализуется на базе магнитных дисков. Информация в ней хранится в виде специальных программно поддерживаемых объектов — файлов (согласно стандарту ISO, файл — это «идентифицированная совокупность экземпляров полностью описанного в конкретной программе типа данных, находящихся вне программы во внешней памяти и доступных программе посредством специальных операций»).

Устройство управления (УУ) — важнейшая часть ВМ, организующая автоматическое выполнение программ (путем реализации функций управления) и обеспечивающая функционирование ВМ как единой системы. Для пояснения функций УУ ВМ следует рассматривать как совокупность элементов, между которыми происходит пересылка информации, в ходе которой эта информация может подвергаться определенным видам обработки. Пересылка информации между любыми элементами ВМ инициируется своим сигналом управления (СУ), то есть управление вычислительным процессом сводится к выдаче нужного набора СУ в нужной временной последовательности. Цепи СУ показаны на рис. 1.3 полутоновыми линиями. Основной функцией УУ является формирование управляющих сигналов, отвечающих за извлечение команд из памяти в порядке, определяемом программой, и последующее исполнение этих команд. Кроме того, УУ формирует СУ для синхронизации и координации внутренних и внешних устройств ВМ.

Еще одной неотъемлемой частью ВМ является арифметико-логическое устройство (АЛУ). АЛУ обеспечивает арифметическую и логическую обработку двух входных переменных, в результате которой формируется выходная переменная. Функции АЛУ обычно сводятся к простым арифметическим и логическим операциям, а также операциям сдвига. Помимо результата операции АЛУ формирует ряд признаков результата (флагов), характеризующих полученный результат и события, произошедшие в процессе его получения (равенство нулю, знак, четность, перенос, переполнение и т. д.). Флаги могут анализироваться в УУ с целью принятия решения о дальнейшей последовательности выполнения команд программы.

УУ и АЛУ тесно взаимосвязаны и их обычно рассматривают как единое устройство, известное как центральный процессор (ЦП) или просто процессор. Помимо УУ и АЛУ в процессор входит также набор регистров общего назначения (РОН), служащих для промежуточного хранения информации в процессе ее обработки.

Типы структур вычислительных машин и систем

Структуры вычислительных машин

Типичным представителем первого способа может служить классическая фон-неймановская ВМ (см. рис. 1.3). В ней между взаимодействующими устройствами (процессор, память, устройство ввода/вывода) имеются непосредственные связи. Особенности связей (число линий в шинах, пропускная способность и т. п.) определяются видом информации, характером и интенсивностью обмена. Достоинством архитектуры с непосредственными связями можно считать возможность развязки «узких мест» путем улучшения структуры и характеристик только определенных связей, что экономически может быть наиболее выгодным решением. У фон-неймановских ВМ таким «узким местом» является канал пересылки данных между ЦП и памятью, и «развязать» его достаточно непросто [56]. Кроме того, ВМ с непосредственными связями плохо поддаются реконфигурации.

В варианте с общей шиной все устройства вычислительной машины подключены к магистральной шине, служащей единственным трактом для потоков команд, данных и управления (рис. 1.4). Наличие общей шины существенно упрощает реализацию ВМ, позволяет легко менять состав и конфигурацию машины. Благодаря этим свойствам шинная архитектура получила широкое распространение в мини- и микроЭВМ. Вместе с тем, именно с шиной связан и основной недостаток архитектуры: в каждый момент передавать информацию по шине может только одно устройство. Основную нагрузку на шину создают обмены между процессором и памятью, связанные с извлечением из памяти команд и данных и записью в память результатов вычислений. На операции ввода/вывода остается лишь часть пропускной способности шины. Практика показывает, что даже при достаточно быстрой шине для 90% приложений этих остаточных ресурсов обычно не хватает, особенно в случае ввода или вывода больших массивов данных.

Рис. 1.4. Структура вычислительной машины на базе общей шины

В целом следует признать, что при сохранении фон-неймановской концепции последовательного выполнения команд программы шинная архитектура в чистом ее виде оказывается недостаточно эффективной. Более распространена архитектура с иерархией шин, где помимо магистральной шины имеется еще несколько дополнительных шин. Они могут обеспечивать непосредственную связь между устройствами с наиболее интенсивным обменом, например процессором и кэш-памятью. Другой вариант использования дополнительных шин — объединение однотипных устройств ввода/вывода с последующим выходом с дополнительной шины на магистральную. Все эти меры позволяют снизить нагрузку на общую шину и более эффективно расходовать ее пропускную способность.

Структуры вычислительных систем

В вычислительных системах с общей памятью (рис. 1.5) имеется общая основная память, совместно используемая всеми процессорами системы. Связь процессоров с памятью обеспечивается с помощью коммуникационной сети, чаще всего вырождающейся в общую шину. Таким образом, структура ВС с общей памятью аналогична рассмотренной выше архитектуре с общей шиной, в силу чего ей свойственны те же недостатки. Применительно к вычислительным системам данная схема имеет дополнительное достоинство: обмен информацией между процессорами не связан с дополнительными операциями и обеспечивается за счет доступа к общим областям памяти.

Рис 1.5. Структура вычислительной системы с общей памятью

Альтернативный вариант организации — распределенная система, где общая память вообще отсутствует, а каждый процессор обладает собственной локальной памятью (рис. 1.6). Часто такие системы объединяют отдельные ВМ. Обмен информацией между составляющими системы обеспечивается с помощью коммуникационной сети посредством обмена сообщениями.

Рис 1.6. Структура распределенной вычислительной системы

Подобное построение ВС снимает ограничения, свойственные для общей шины, но приводит к дополнительным издержкам на пересылку сообщений между процессорами или машинами.

Перспективы совершенствования архитектуры ВМ и ВС

Совершенствование архитектуры вычислительных машин и систем началось с момента появления первых ВМ и не прекращается по сей день. Каждое изменение в архитектуре направлено на абсолютное повышение производительности или, по крайней мере, на более эффективное решение задач определенного класса. Эволюцию архитектур определяют самые различные факторы, главные из которых показаны на рис. 1.7. Не умаляя роли ни одного из них, следует признать, что наиболее очевидные успехи в области средств вычислительной техники все же связаны с технологическими достижениями. Характер и степень влияния прочих факторов подробно описаны в [120] и в данном учебнике не рассматриваются.

Рис. 1.7. Факторы, определяющие развитие архитектуры вычислительных систем

С каждым новым технологическим успехом многие из архитектурных идей переходят на уровень практической реализации. Очевидно, что процесс этот будет продолжаться и в дальнейшем, однако возникает вопрос: «Насколько быстро?» Косвенный ответ можно получить, проанализировав тенденции совершенствования технологий, главным образом полупроводниковых.

Тенденции развития больших интегральных схем

Наиболее перспективным представляется увеличение размеров кристалла, однако только на первый взгляд. Кристаллической подложкой микросхемы служит тонкая пластина, представляющая собой срез цилиндрического бруска полупроводникового материала. Полезная площадь подложки ограничена вписанным в окружность квадратом или прямоугольником. Увеличение диаметра кристаллической подложки на 10% на практике позволяет получить до 60% прироста числа транзисторов на кристалле. К сожалению, технологические сложности, связанные с изготовлением кристаллической подложки большого размера без ухудшения однородности ее свойств по всей поверхности, чрезвычайно велики. Фактические тенденции в плане увеличения размеров кристаллической подложки СБИС иллюстрирует рис. 1.8.

Точки излома на графике соответствуют годам, когда переход на новый размер кристалла становится повсеместным. Каждому переходу обычно предшествуют 2–3-летние исследования, а собственно переход на пластины увеличенного диаметра происходит в среднем один раз в 9 лет.

Рис. 1.8. Тенденции увеличения диаметра кристаллической подложки СБИС

Пока основные успехи в плане увеличения емкости СБИС связаны с уменьшением размеров элементарных транзисторов и плотности их размещения на кристалле. Здесь тенденции эволюции СБИС хорошо описываются эмпирическим законом Мура [168]. В 1965 году Мур заметил, что число транзисторов, которое удается разместить на кристалле микросхемы, удваивается каждые 12 месяцев. Он предсказал, что эта тенденция сохранится в 70-е годы, а начиная с 80-х темп роста начнет спадать. В 1995 году Мур уточнил свое предсказание, сделав прогноз, что удвоение числа транзисторов далее будет происходить каждые 24 месяца.

Создание интегральных микросхем предполагает два этапа. Первый из них носит название литографии и заключается в получении маски, определяющей структуру будущей микросхемы. На втором этапе маска накладывается на полупроводниковую пластину, после чего пластина облучается, в результате чего и формируется микросхема. Уменьшение размеров элементов на кристалле напрямую зависит от возможностей технологии (рис. 1.9).

Рис 1.9. Размер минимального элемента на кристалле интегральной микросхемы

Современный уровень литографии сделал возможным серийный выпуск СБИС, в которых размер элемента не превышает 0,13 мкм. Чтобы оценить перспективы развития возможностей литографии на ближайший период, обратимся к прогнозу авторитетного эксперта в области полупроводниковых технологий — International Technology Roadmap for Semiconductors. Результаты прогноза относительно будущих достижений литографии, взятые из отчета за 2001 год [185], приведены на рис. 1.10.

Рис. 1.10. Прогноз максимальных размеров элементов на кристалле СБИС

Наконец, еще одна общая тенденция в технологии СБИС — переход от алюминиевых соединительных линий на кристалле на медные. «Медная» технология позволяет повысить быстродействие СБИС примерно на 10% с одновременным снижением потребляемой мощности.

Приведенные выше закономерности определяют общие направления совершенствования технологий СБИС. Для более объективного анализа необходимо принимать во внимание функциональное назначение микросхем. В аспекте архитектуры ВМ и ВС следует отдельно рассмотреть «процессорные» СБИС и СБИС запоминающих устройств.

Тенденции развития элементной базы процессорных устройств

Увеличение размеров кристаллов процессорных СБИС происходит в соответствии с ранее рассмотренными общими тенденциями и не имеет каких-либо особенностей.

Плотность упаковки логических элементов в процессорных СБИС принято оценивать количеством транзисторов, из которых, собственно, и строятся логические схемы процессора. Общие тенденции в плане плотности упаковки проследим на примере линейки микропроцессоров фирмы Intel (рис. 1.11). Из рисунка видно, что количество транзисторов в микропроцессорах, выпущенных до 2002 года, хорошо согласуется с законом Мура. Та же закономерность прослеживается и для других типов процессорных СБИС. Достаточно близки и абсолютные показатели разных микропроцессоров, выпущенных приблизительно в один и тот же период. Так, микропроцессор Pentium 4 фирмы Intel содержит 42 млн транзисторов, а микропроцессор Athlon XL фирмы AMD — 37 млн.

Чтобы оценить перспективы роста плотности упаковки на ближайшие два десятилетия, на рис. 1.11 дополнительно приведены прогностические данные на пе-

Рис. 1.11. Тенденции увеличения количества транзисторов на кристаллах процессорных СБИС

риод до 2020 года, взятые из [185]. Нетрудно заметить, что прогноз также не слишком расходится с уточненным законом Мура. Общий итог можно сформулировать следующим образом: плотность упаковки логических схем процессорных СБИС каждые два года будет возрастать вдвое.

В качестве параметра, характеризующего быстродействие логических схем процессорных СБИС, обычно используют так называемую внутреннюю тактовую частоту. На рис. 1.12 показаны значения тактовых частот микропроцессоров фирмы Intel. Из графика видно стремление к росту внутренней тактовой частоты процессорных СБИС: удвоение частоты происходит в среднем каждые два года. На рисунке присутствует также прогноз на ближайший период (данные взяты из [185]), из которого явствует, что в ближайшем будущем темп увеличения внутренней тактовой частоты может несколько снизиться.

Рис. 1.12. Тенденции увеличения внутренней тактовой частоты процессорных СБИС

Тенденции развития полупроводниковых запоминающих устройств

По мере повышения возможностей вычислительных средств растут и «аппетиты» программных приложений относительно емкости основной памяти. Эту ситуацию отражает так называемый закон Паркинсона: «Программное обеспечение увеличивается в размерах до тех пор, пока не заполнит всю доступную на данный момент память». В цифрах тенденция возрастания требований к емкости памяти выглядит так: увеличение в полтора раза каждые два года. Основная память современных ВМ и ВС формируется из СБИС полупроводниковых запоминающих устройств, главным образом динамических ОЗУ. Естественные требования к таким СБИС: высокие плотность упаковки запоминающих элементов и быстродействие, низкая стоимость.

Плотность упаковки запоминающих элементов на кристалле динамического ОЗУ принято характеризовать емкостью хранимой информации в битах. Представление о современном состоянии и перспективах на ближайшее будущее дает график, приведенный на рис. 1.13. Для СБИС памяти также подтверждается справедливость закона Мура и предсказанное им уменьшение темпов повышения плотности упаковки. В целом можно предсказать, что число запоминающих элементов на кристалле будет возрастать в два раза каждые полтора года.

Рис. 1.13. Тенденции увеличения количества запоминающих элементов на кристалле СБИС динамических запоминающих устройств

Рис. 1.14. Разрыв в производительности процессоров и динамических запоминающих устройств

С быстродействием СБИС памяти дело обстоит хуже. Высокая скорость процессоров уже давно находится в противоречии с относительной медлительностью запоминающих устройств основной памяти. Проблема постоянно усугубляется несоответствием темпов роста тактовой частоты процессоров и быстродействия памяти, и особых перспектив в этом плане пока не видно, что иллюстрирует рис. 1.14.

Абсолютные темпы снижения длительности цикла памяти, начиная с 1980 года, показаны на рис. 1.15. Общая тенденция: на двукратное уменьшение длительности цикла динамического ЗУ уходит примерно 15 лет.

Рис. 1.15. Быстродействие микросхем динамической памяти

В плане снижения стоимости СБИС памяти перспективы весьма обнадеживающие (рис. 1.16). В течение достаточно длительного времени стоимость в пересчете на один бит снижается примерно на 25–40% в год.

Рис. 1.16. Тенденции снижения стоимости СБИС динамической памяти в пересчете на 1 Мбит

Перспективные направления исследований в области архитектуры

Основные направления исследований в области архитектуры ВМ и ВС можно условно разделить на две группы: эволюционные и революционные. К первой группе следует отнести исследования, целью которых является совершенствование методов реализации уже достаточно известных идей. Изыскания, условно названные революционными, направлены на создание совершенно новых архитектур, принципиально отличных от уже ставшей традиционной фон-неймановской архитектуры.

Большинство из исследований, относимых к эволюционным, связано с совершенствованием архитектуры микропроцессоров (МП). В принципе кардинально новых архитектурных подходов в микропроцессорах сравнительно мало. Основные идеи, лежащие в основе современных МП, были выдвинуты много лет тому назад, но из-за несовершенства технологии и высокой стоимости реализации нашли применение только в больших универсальных ВМ (мэйнфреймах) и суперЭВМ. Наиболее значимые из изменений в архитектуре МП связаны с повышением уровня параллелизма на уровне команд (возможности одновременного выполнения нескольких команд). Здесь в первую очередь следует упомянуть конвейеризацию, суперскалярную обработку и архитектуру с командными словами сверхбольшой длины (VLIW). После успешного переноса на МП глобальных архитектурных подходов «больших» систем основные усилия исследователей теперь направлены на частные архитектурные изменения. Примерами таких эволюционных архитектурных изменений могут служить: усовершенствованные методы предсказания переходов в конвейере команд, повышение частоты успешных обращений к кэш-памяти за счет усложненных способов буферизации и т. п.

Наблюдаемые нами достижения в области вычислительных средств широкого применения пока обусловлены именно «эволюционными» исследованиями. Однако уже сейчас очевидно, что, оставаясь в рамках традиционных архитектур, мы довольно скоро натолкнемся на технологические ограничения. Один из путей преодоления технологического барьера лежит в области нетрадиционных подходов. Исследования, проводимые в этом направлении, по нашей классификации отнесены к «революционным». Справедливость такого утверждения подтверждается первыми образцами ВС с нетрадиционной архитектурой.

Оценивая перспективы эволюционного и революционного развития вычислительной техники, можно утверждать, что на ближайшее время наибольшего прогресса можно ожидать на пути использования идей параллелизма на всех его уровнях и создания эффективной иерархии запоминающих устройств.